04 The Processor Pt1

1 Introduction#

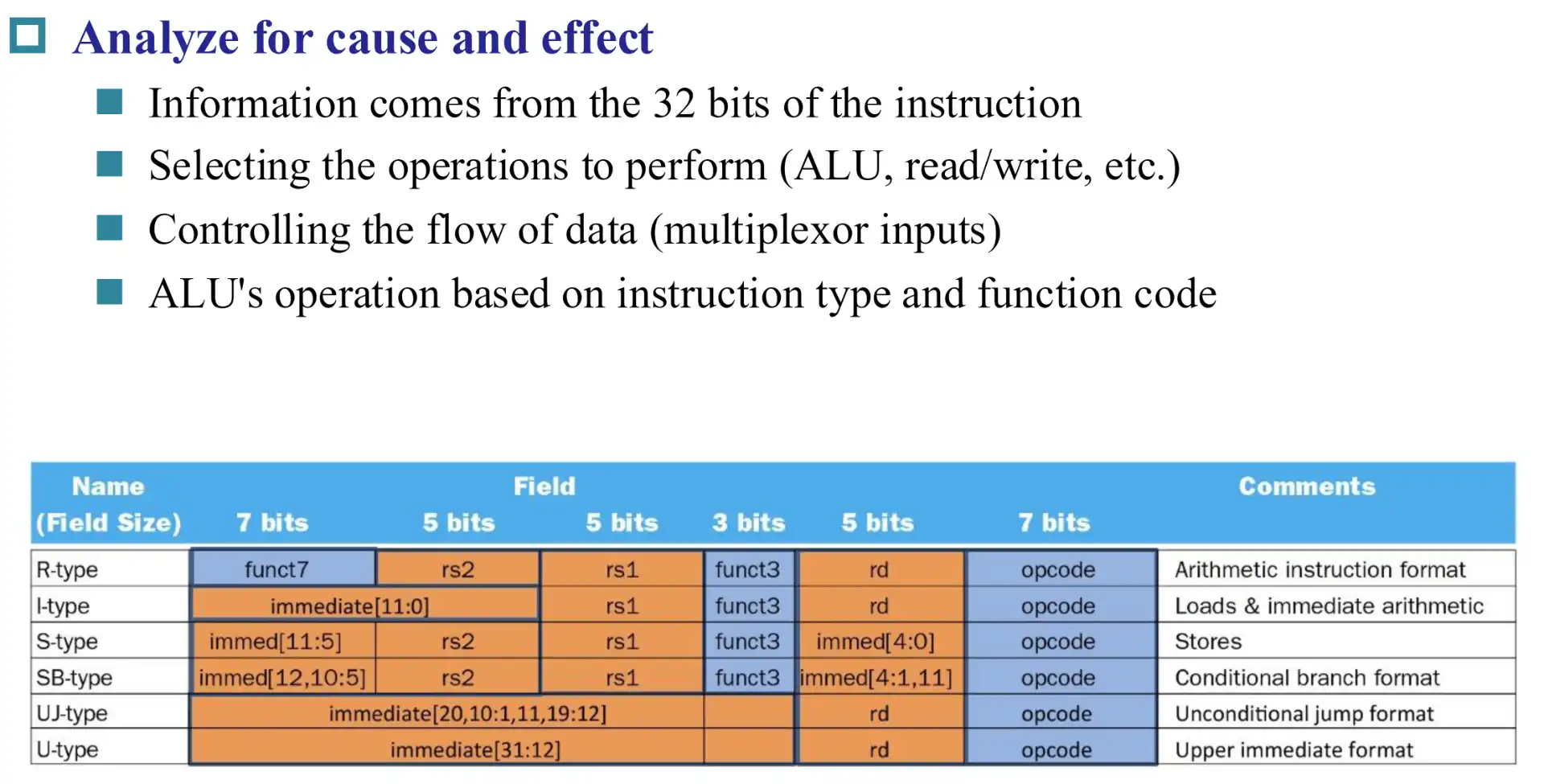

- 在指令进入寄存器模块前,不需要进行解码,因为 RISC-V 中不同指令的

rd, rs1, rs2的相对位置完全一致,除了立即数,本图缺少了ImmGen模块。 Contorl信号控制所有的 MUX,以及模块的使能信号- CPUTime 取决于频率和 CPI,Cycle 小可能导致 CPI 增大

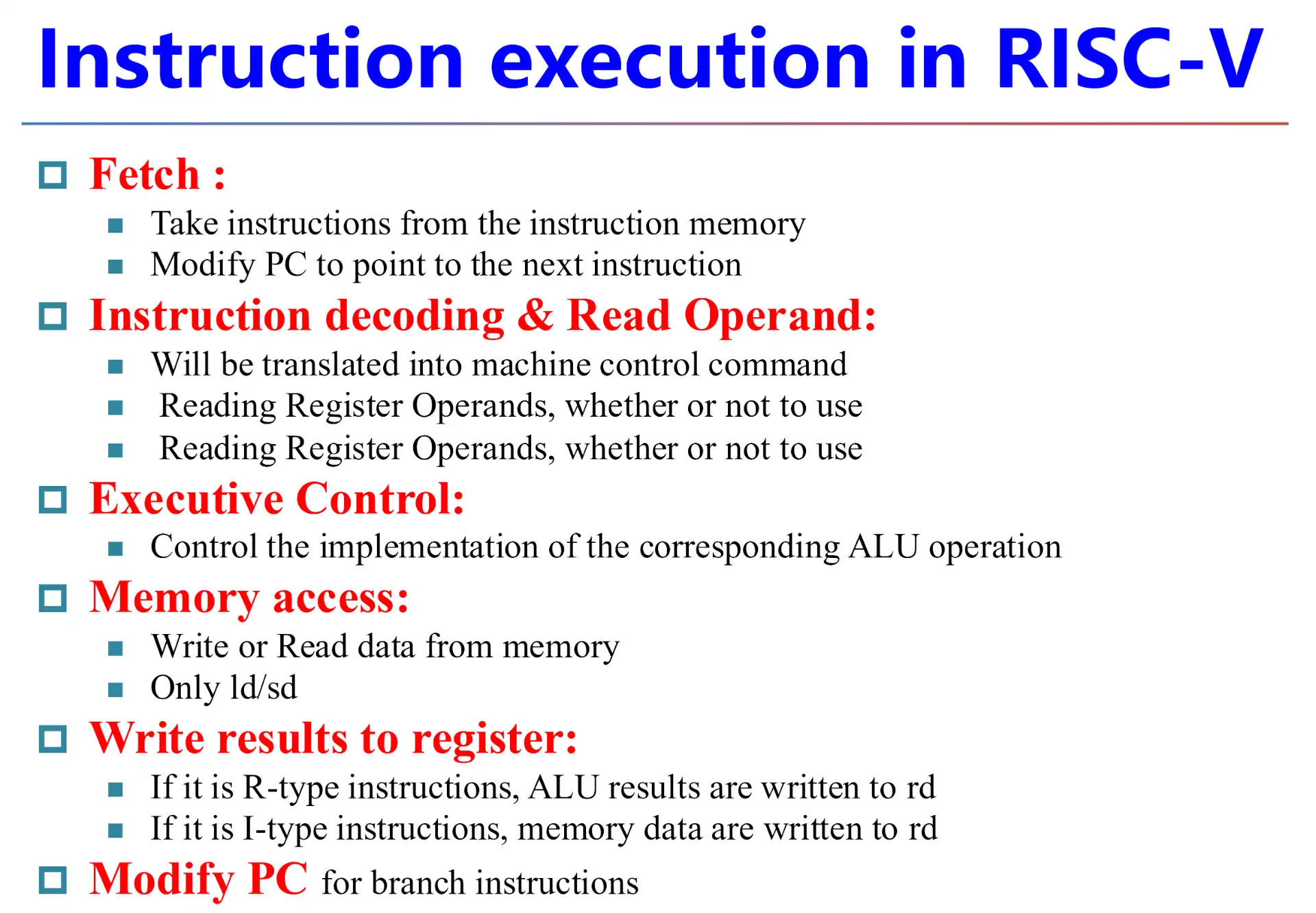

2 Datapath#

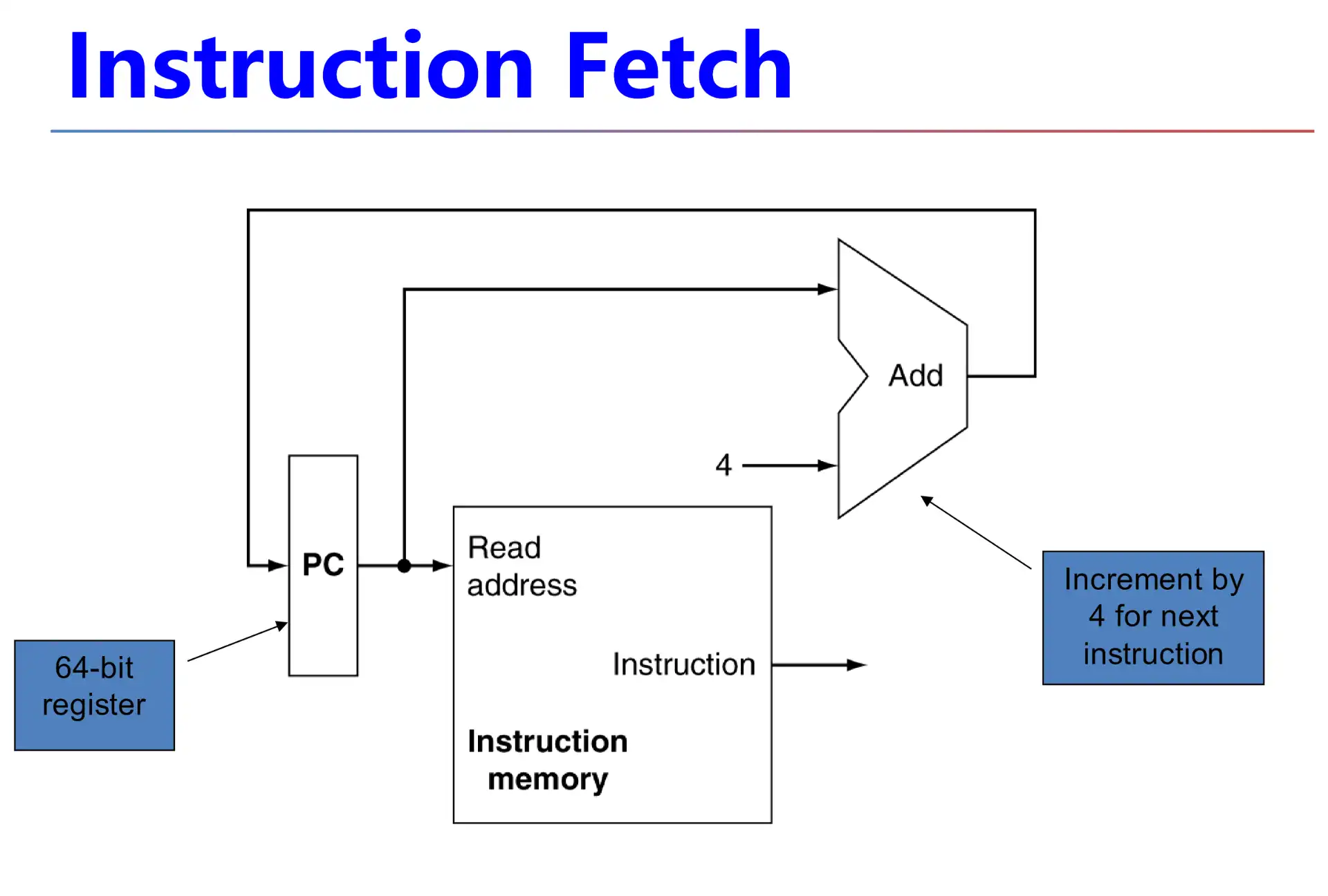

- Modify PC 是旁路,剩下五个是标准步骤,明确某种指令对应的最小需要单元

- Fetch inst mem

- Inst decoding & read operand,执行速度快,同步进行

- Executive Control, ALU operations

- Mem access,不是所有指令都需要访存,

ld/sd - Write to reg, R/I

2.1 不同指令使用的模块#

2.1.1 Fetch#

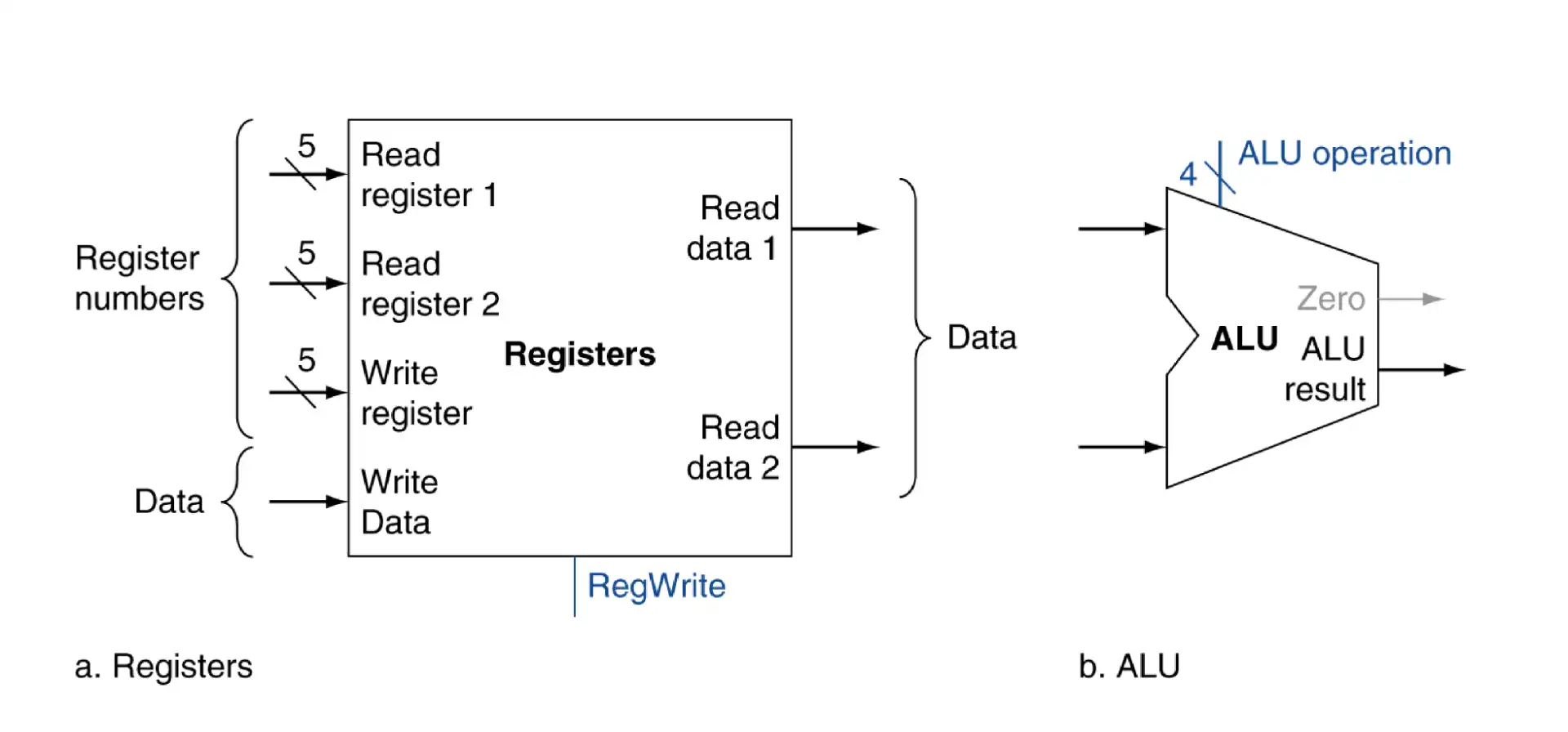

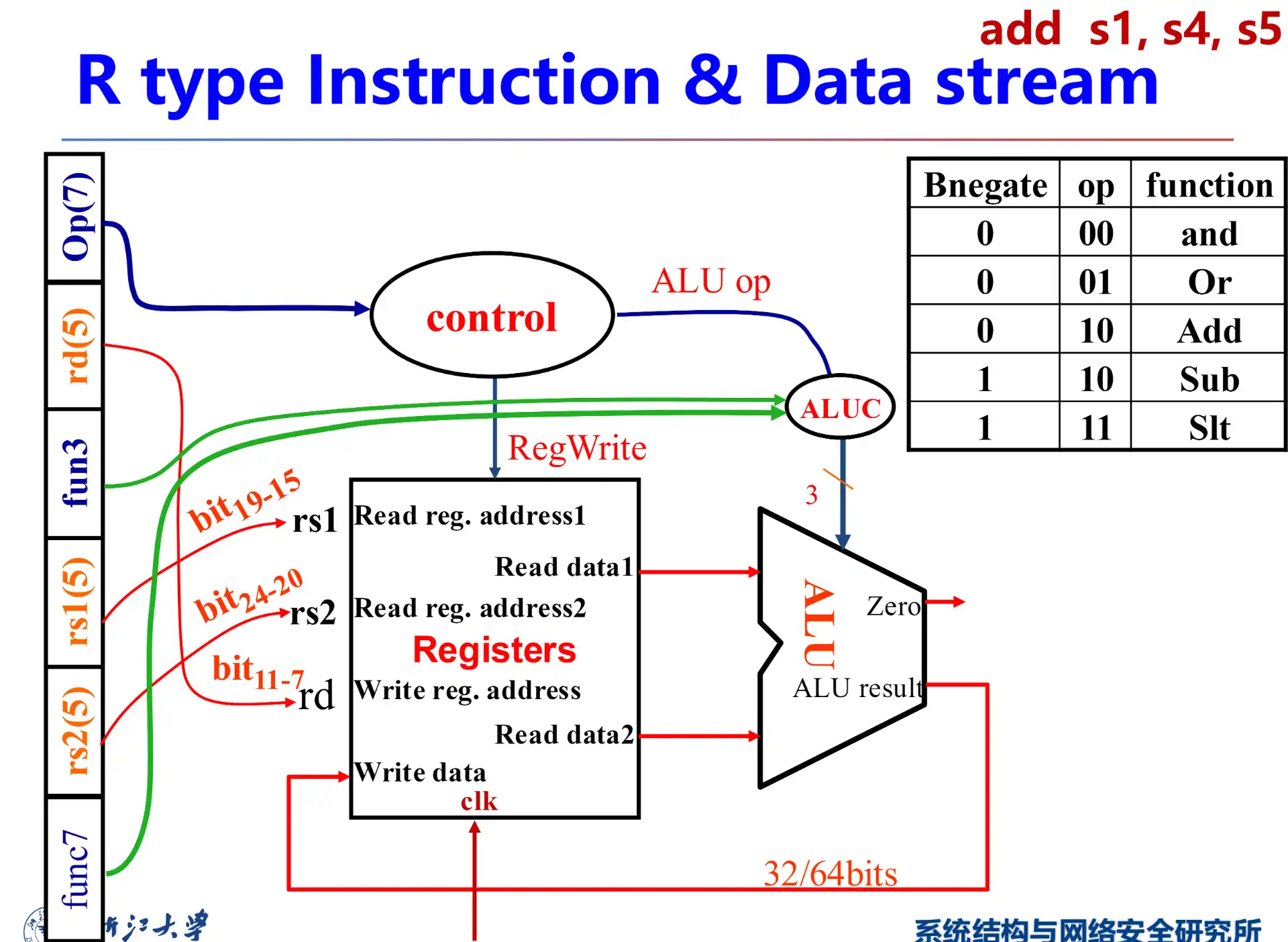

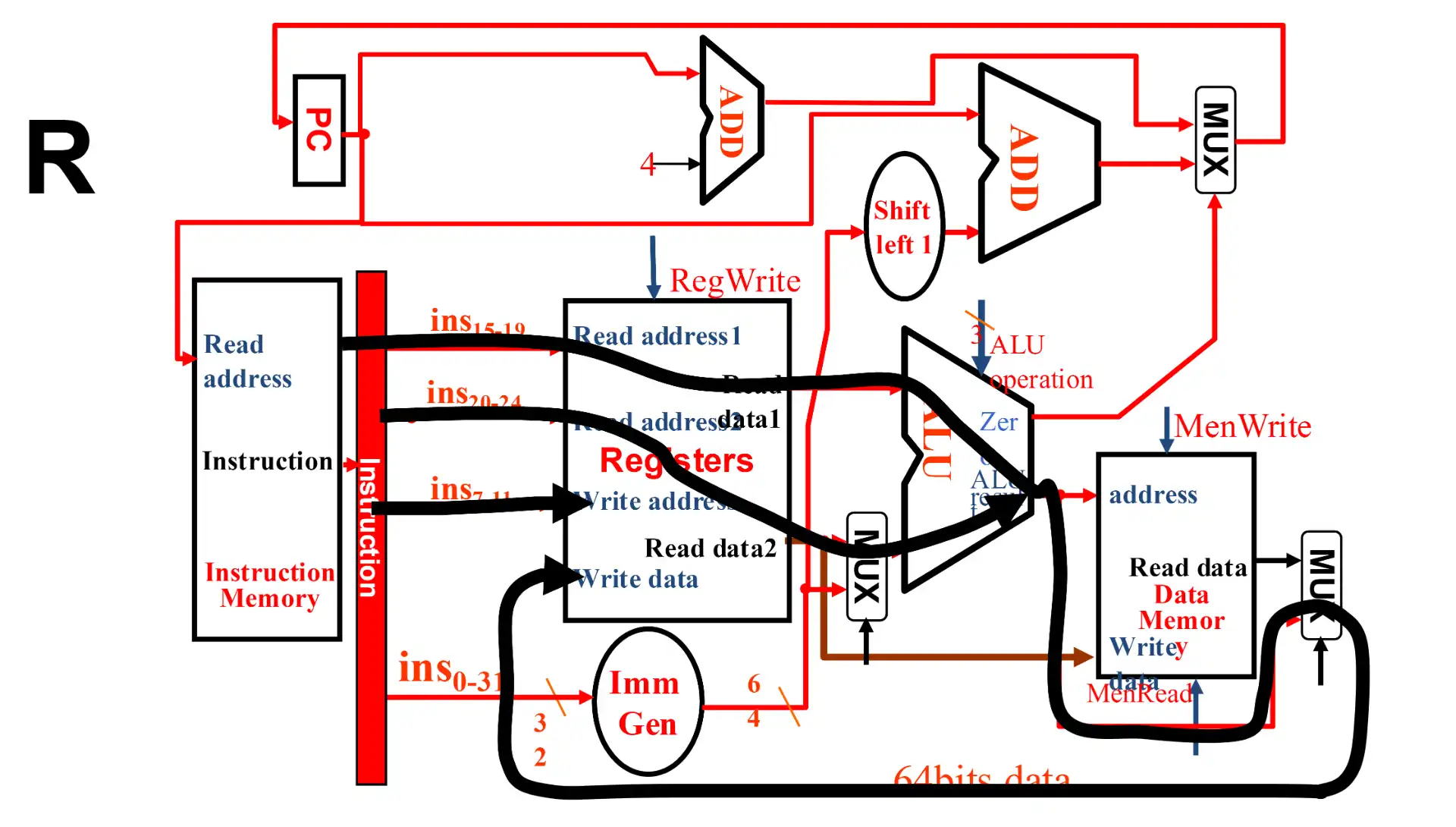

2.1.2 R-Type#

- Read two reg operands

- Perform ALU operation, arithmetic/logical

- Write result to reg

- 注意 RISC-V 中

ALUop是 4 bit 的,因为实现了更多功能 reg的信号要求rs1, rs2rd信号保持RegWrite = 1'b1

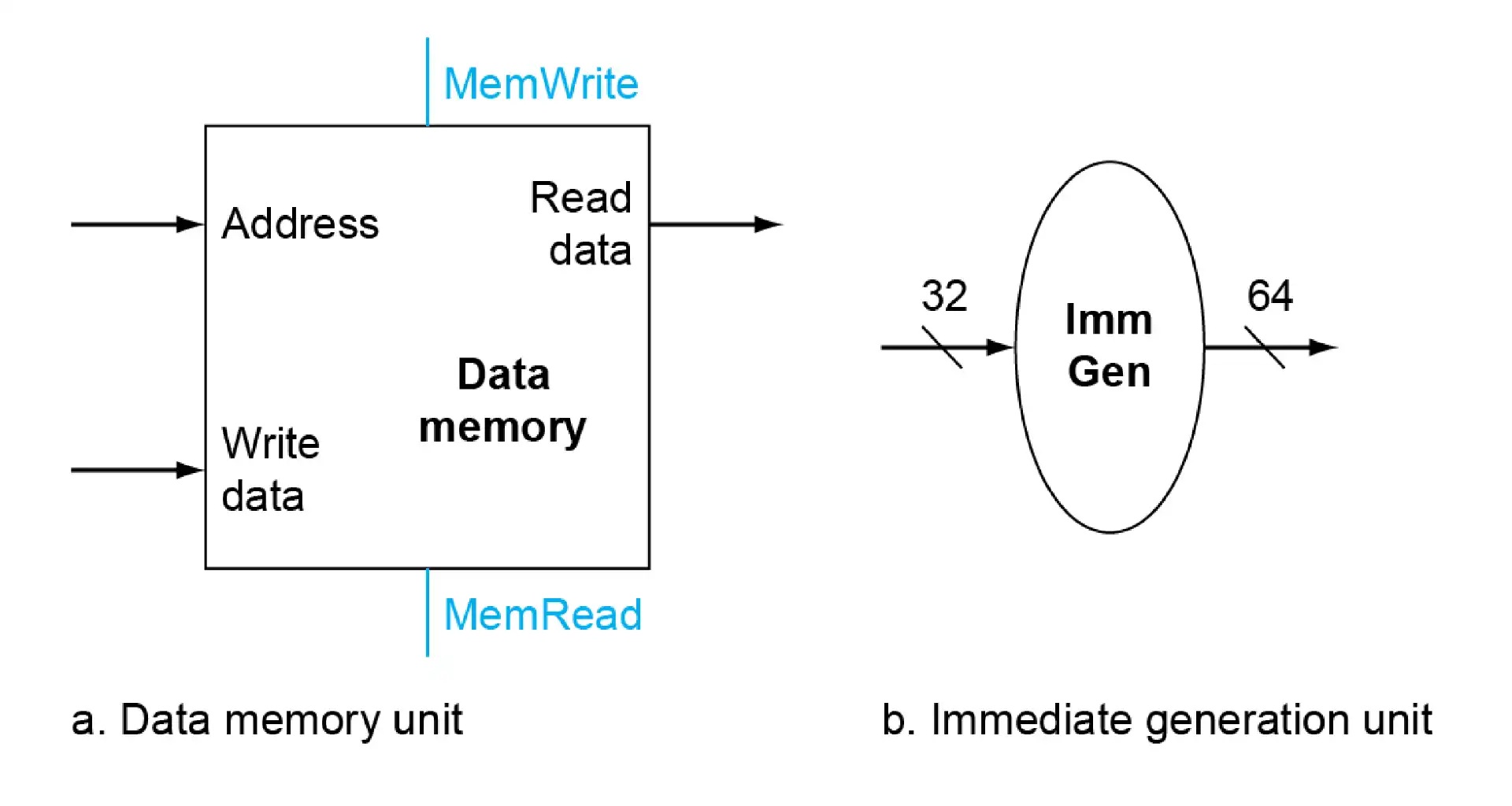

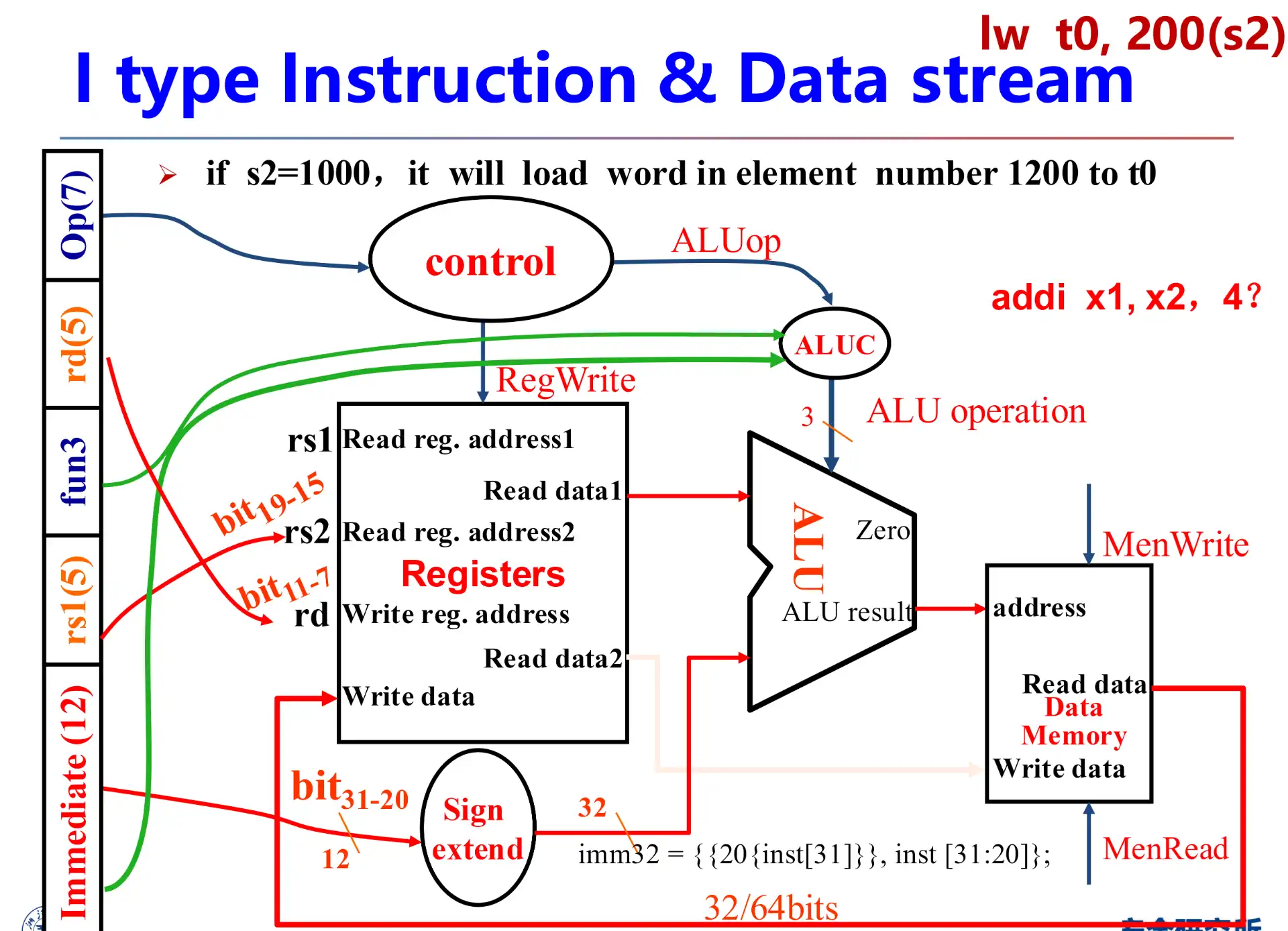

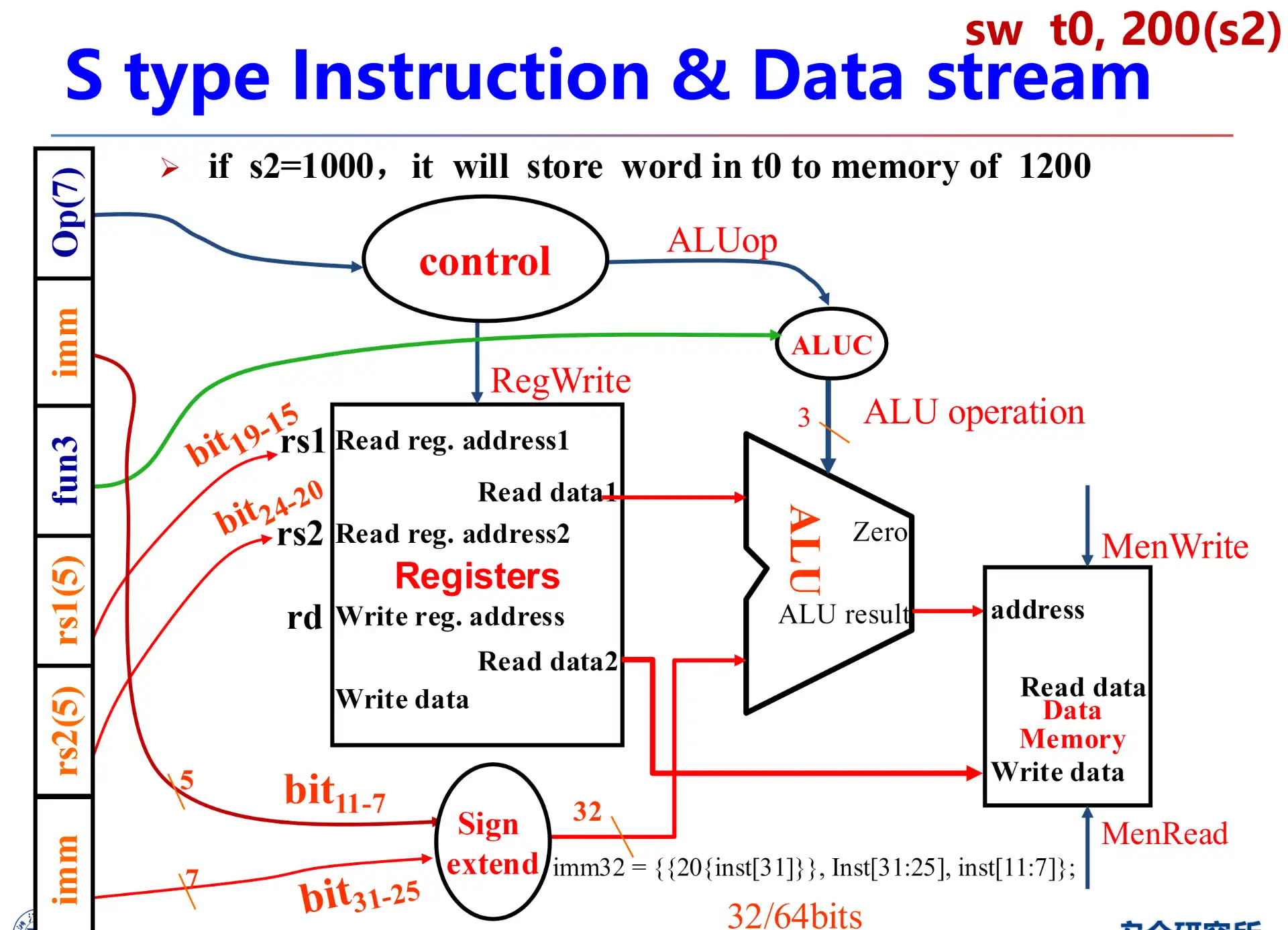

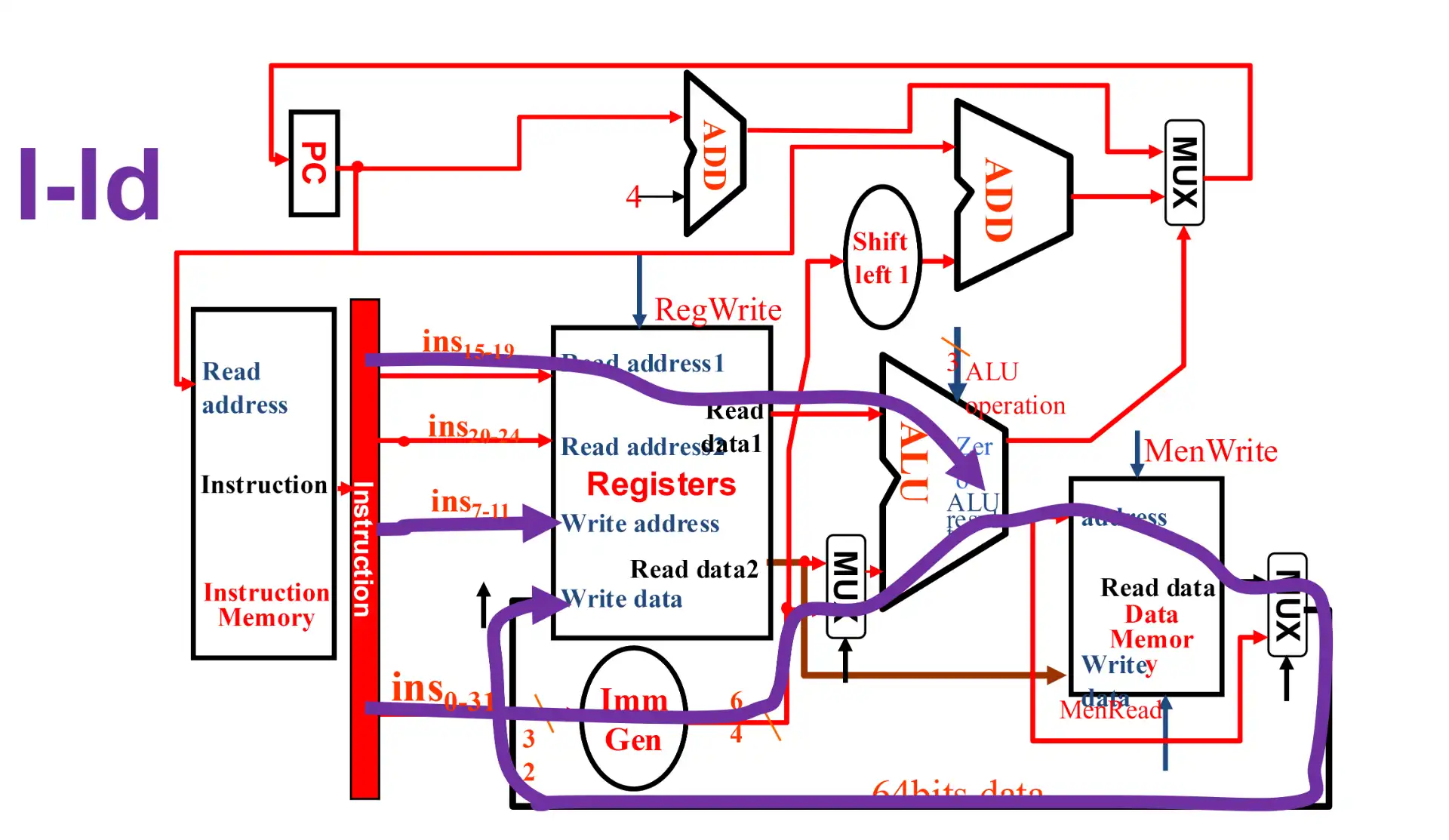

2.1.3 Load/Store#

- Read reg operands

- Calculate address, use ALU, 12-bit offset, sign extened

- Read/Write reg/mem

- 由于内存访问开销较大,设计

MemRead来避免不可控的访存 ImmGen的输入就是inst,要针对不同类型的指令提取/重组立即数,并进行 sign extend

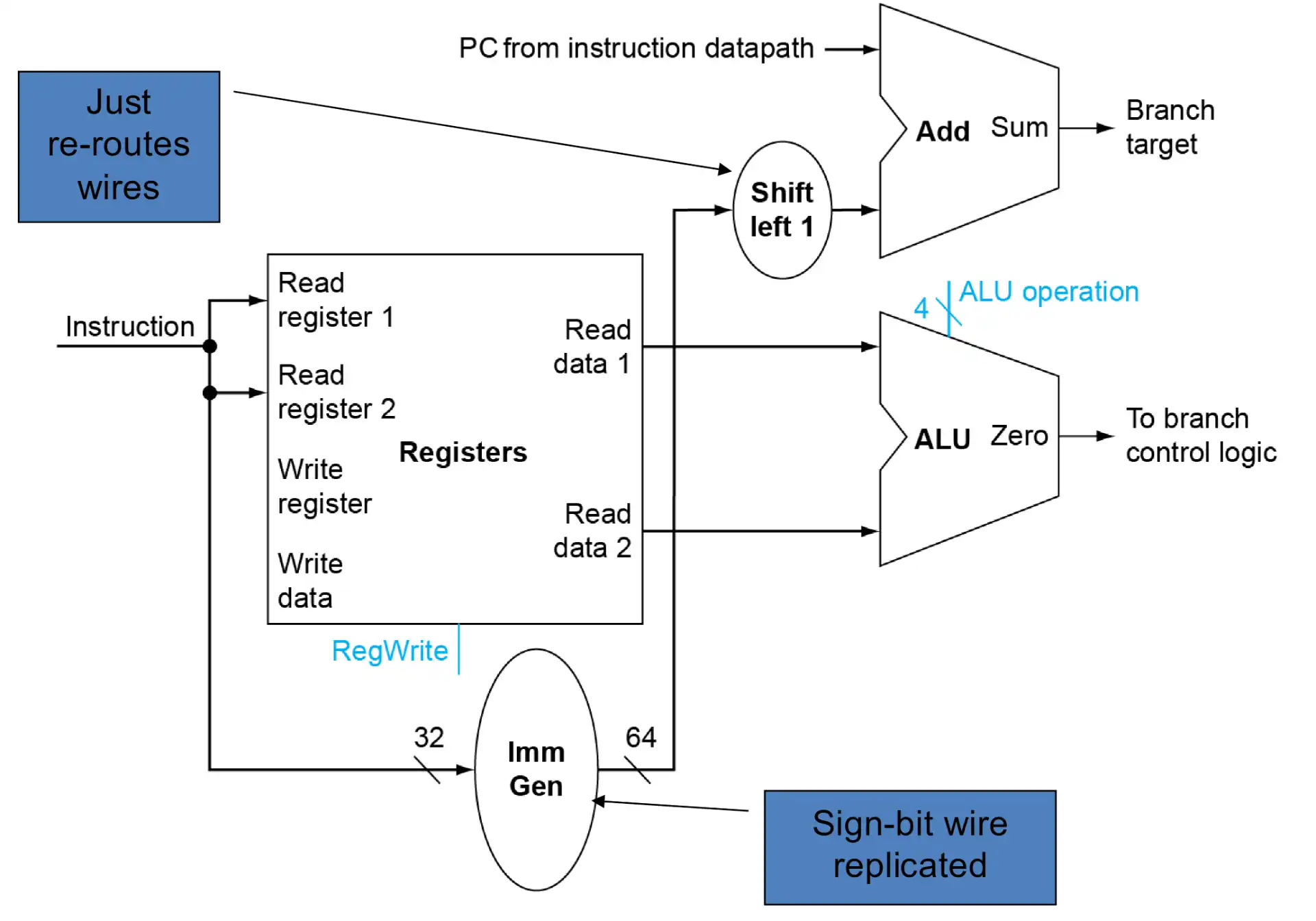

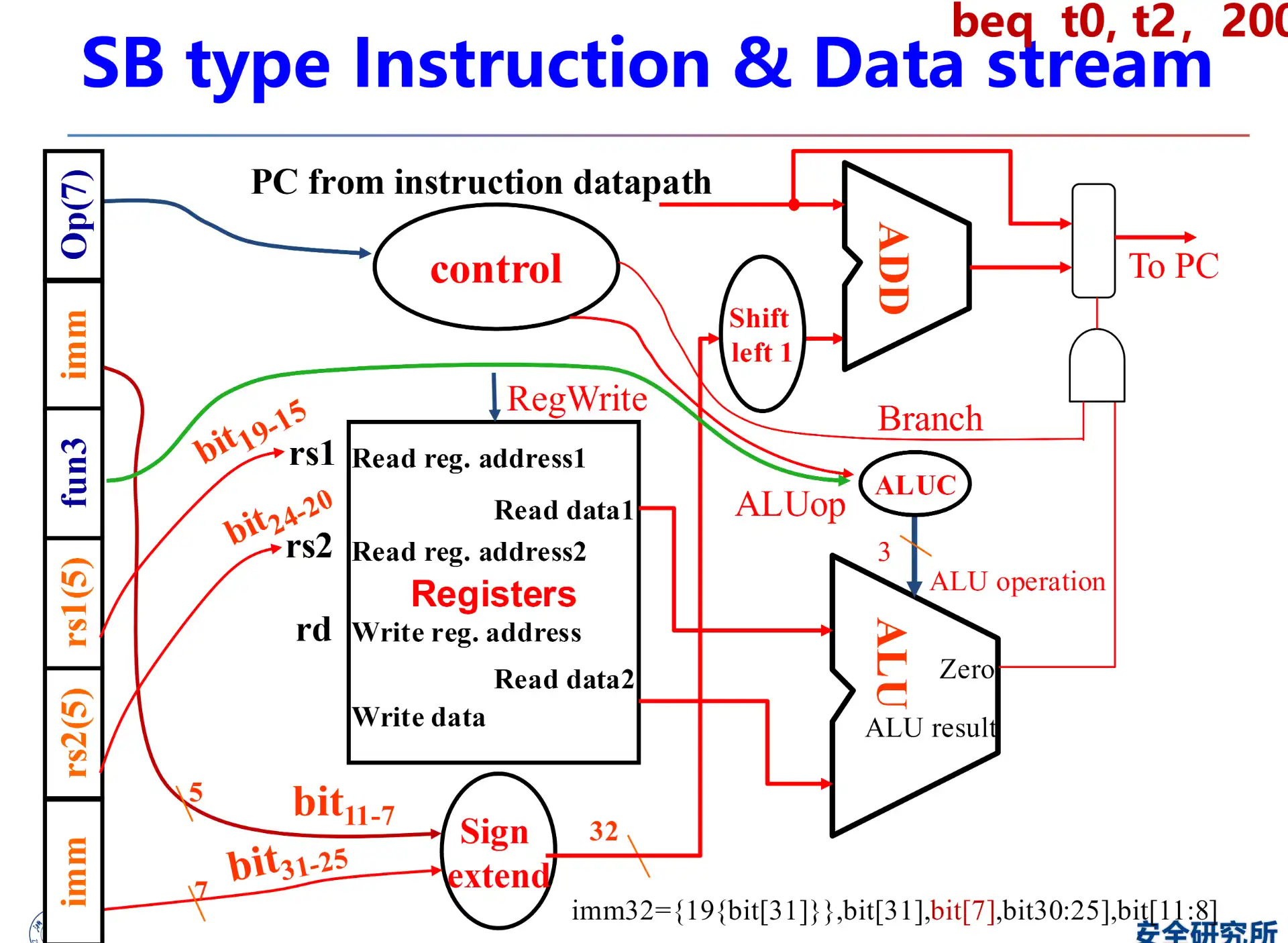

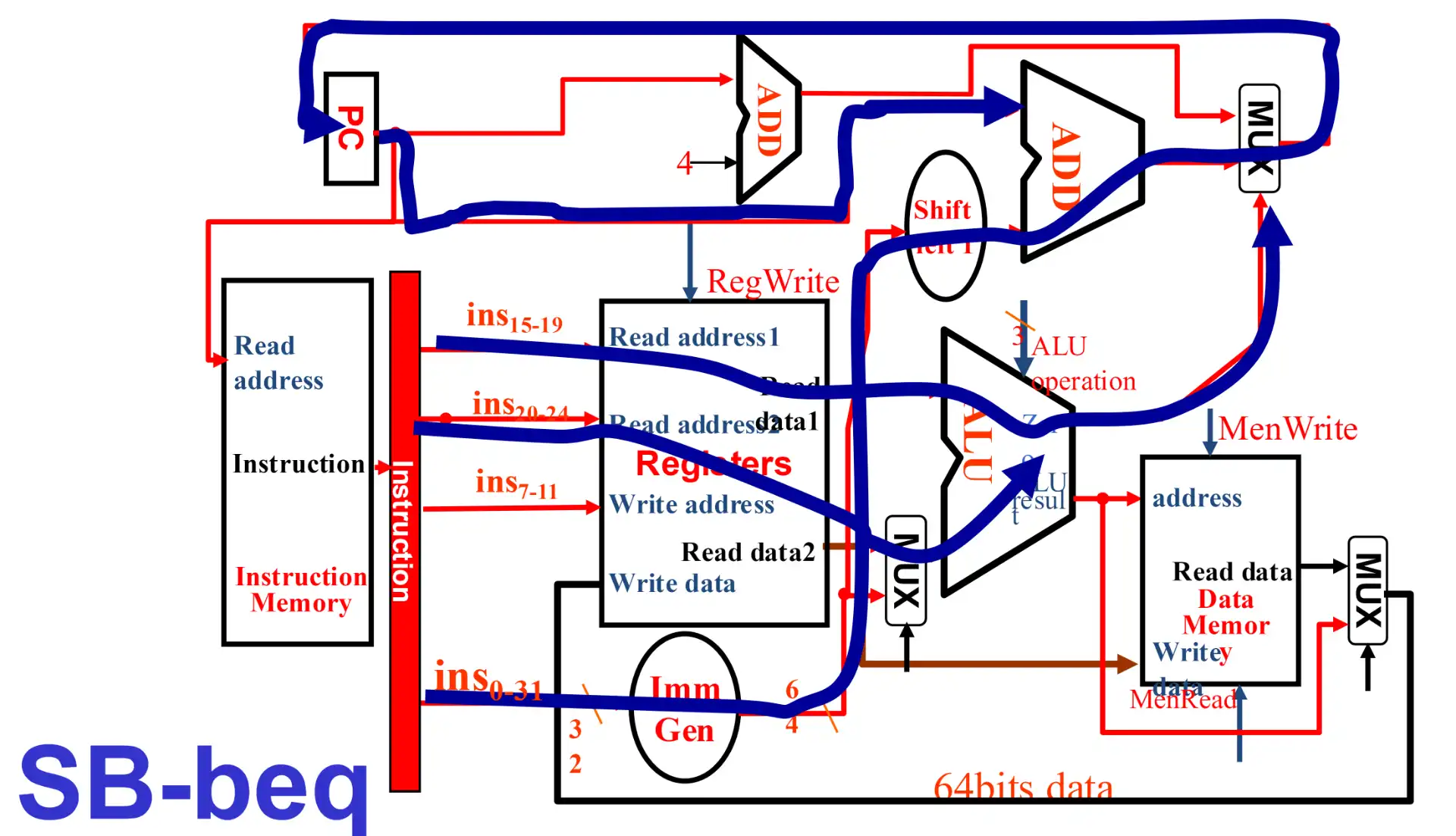

2.1.4 Branch#

- Read reg operands

- Compare operands

- ALU zero output

- Calculate target address

- sign-extend displacement

- shift left 1

- add to PC value

- offset 左移是在电路里完成的,产生了 offset * 2 的效果,但是在写代码的时候不需要考虑,编译器会处理好

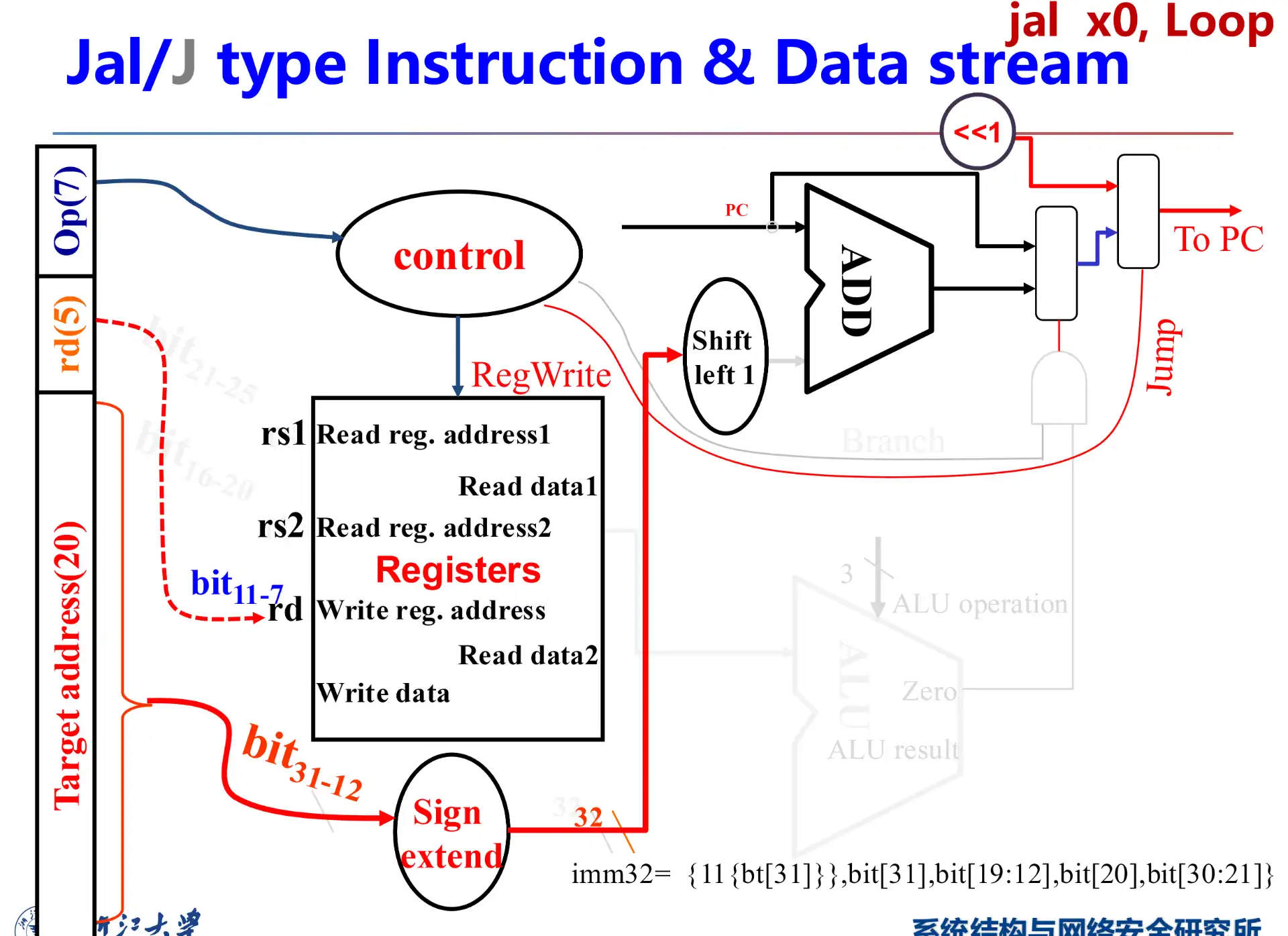

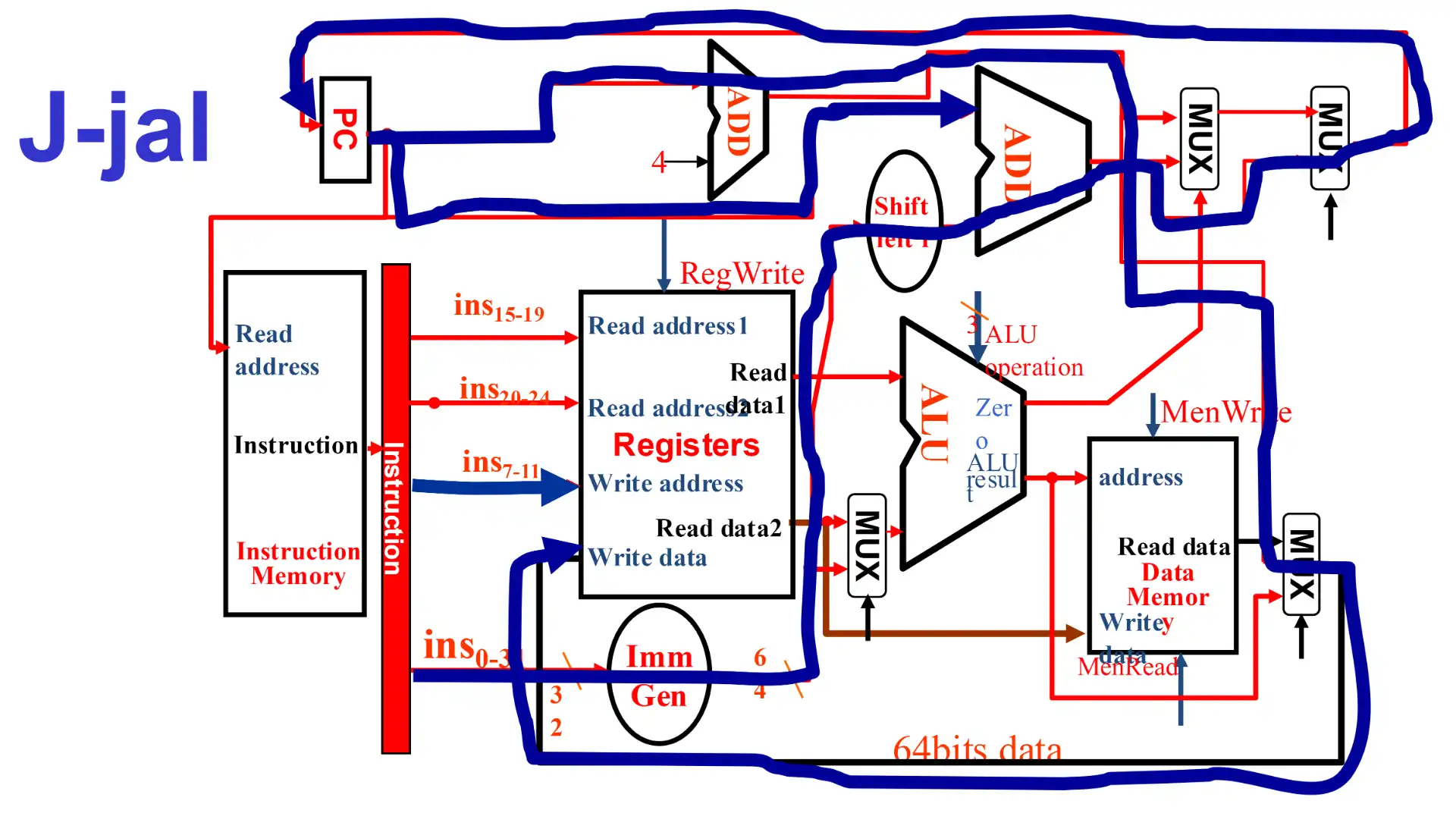

jal没有用到 ALU,因为不需要跳转条件,但是也用到了寄存器,因为保存了return address

2.2 连线题#

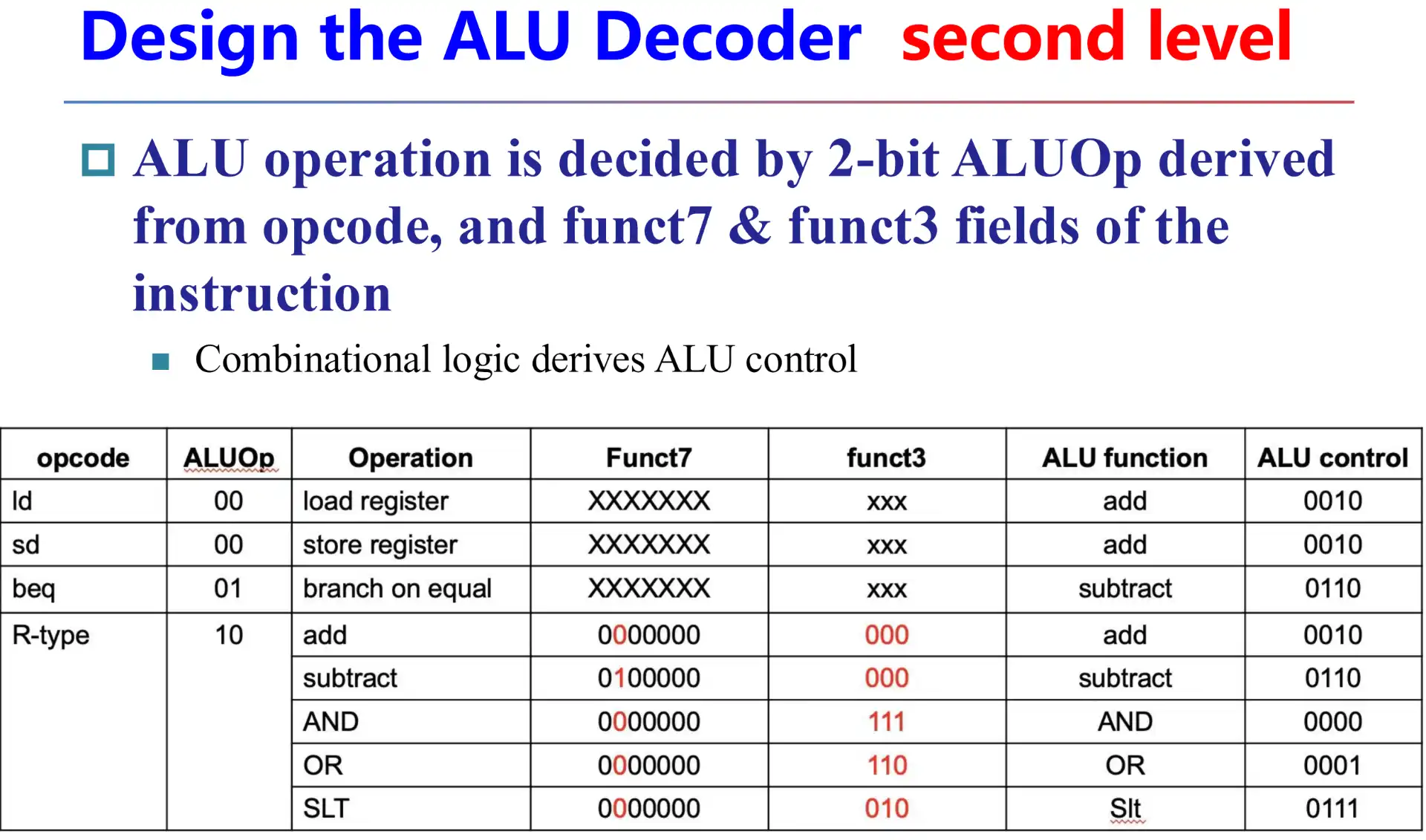

- ALUC 就是

ALUControl,将fun7, fun3单独解码有利于加快速度 ALUop[1:0]-

图中的

ALUC输出应该是 4-bit

-

图中

rs1连错了 -

图中 Sign extend 应该是

ImmGen模块 -

这张图错误太多了

改成 addi

- 将 ALU result 接到 reg write data

- 让 MemWrite MemRead 都为 0

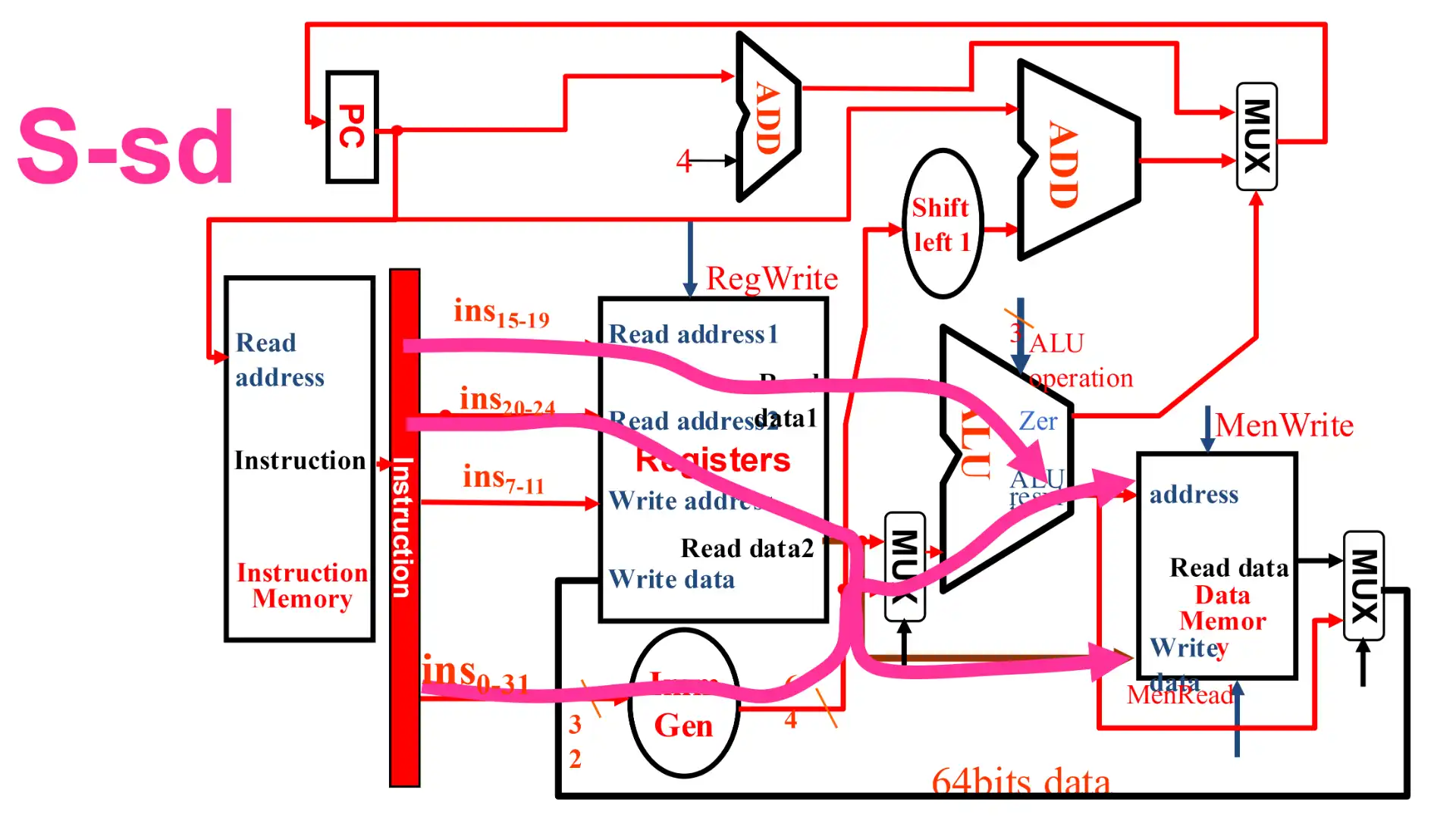

RegWrite = MemRead = 0, MemWrite = 1

-

图中 Sign extend 应该为

ImmGen -

图中右上角的 MUX 第一个输入应该为

PC+4

-

这张图不完整,直接 loop 了,没有保存

return addres -

图中的 Sign extend 应该为

ImmGen -

应该为

PC+4 - 无条件跳转不需要 ALU

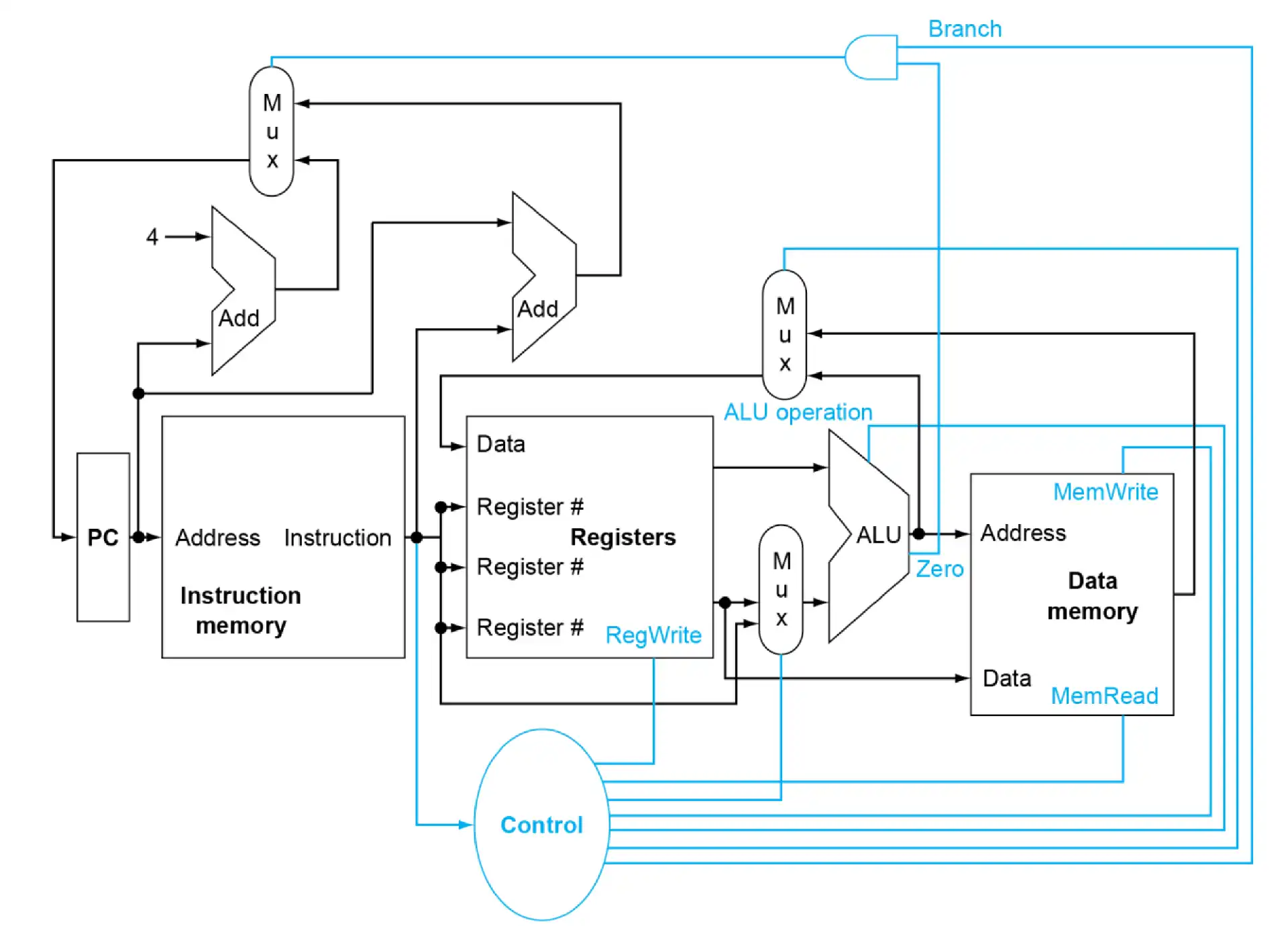

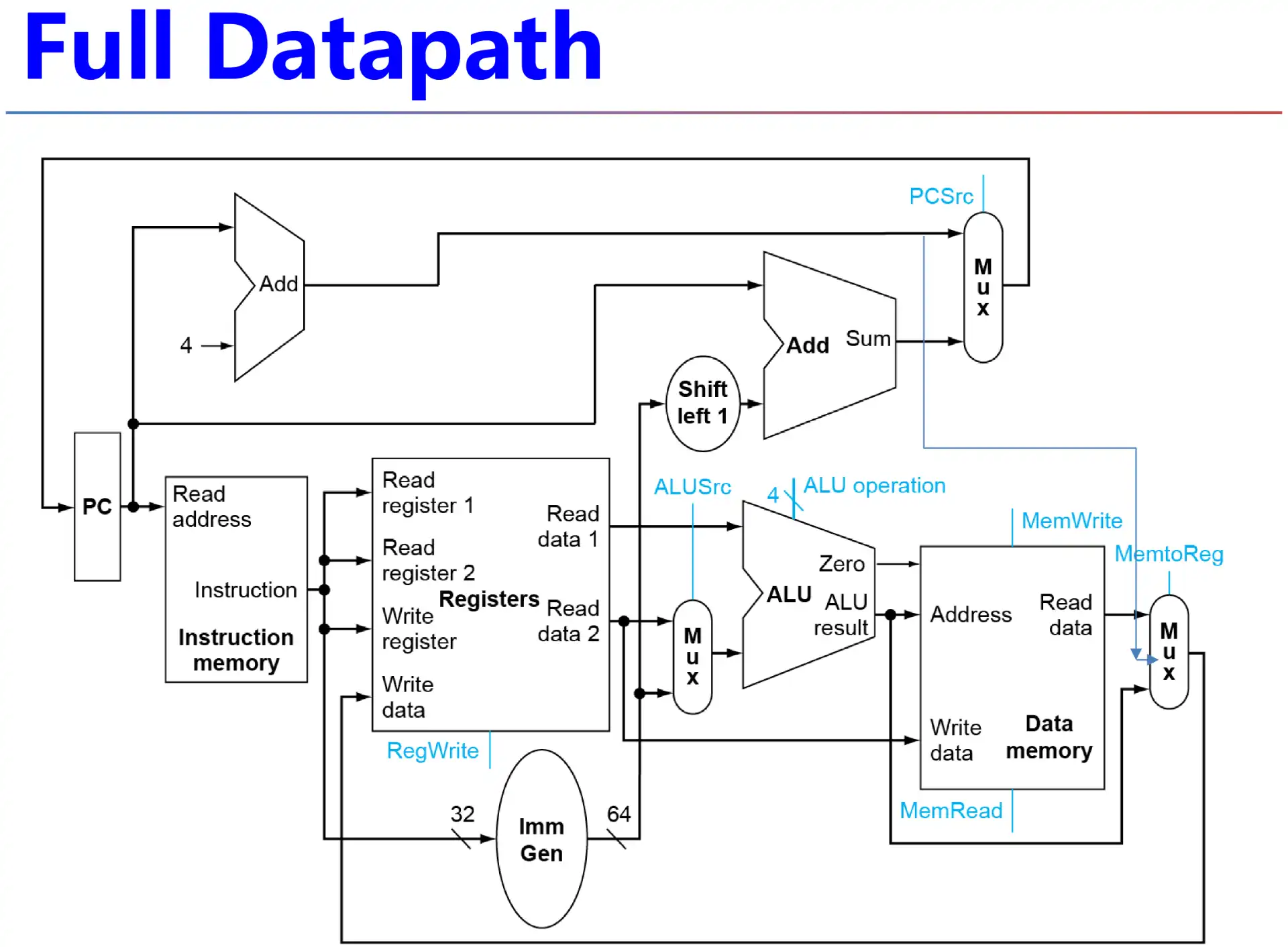

2.3 Full Datapath#

- 三个控制信号

ALUSrc决定 operand2 是rs2还是immPCSrc决定PC是用PC+4还是跳转地址MemtoReg决定 reg write 用 mem 还是ALUresult

- 五个步骤

- inst fetch

- decode & reg read

- execute

- mem

- write to reg

2.4 不同指令的数据通路#

ALUSrc只能取ImmMemtoReg这个 MUX 取任何值都可以,反正RegWrite = 0

PCSrc = Branch & ALU_zero

jal做了两件事情- 将

PC+4存入rd,需要经过MemtoReg,于是需要换成 2-bit 控制信号 - 跳到

PC+offset,不用经过 ALU

- 将

ALUSrc, ALUOperation可以随便选,ALU 输入输出没有任何影响

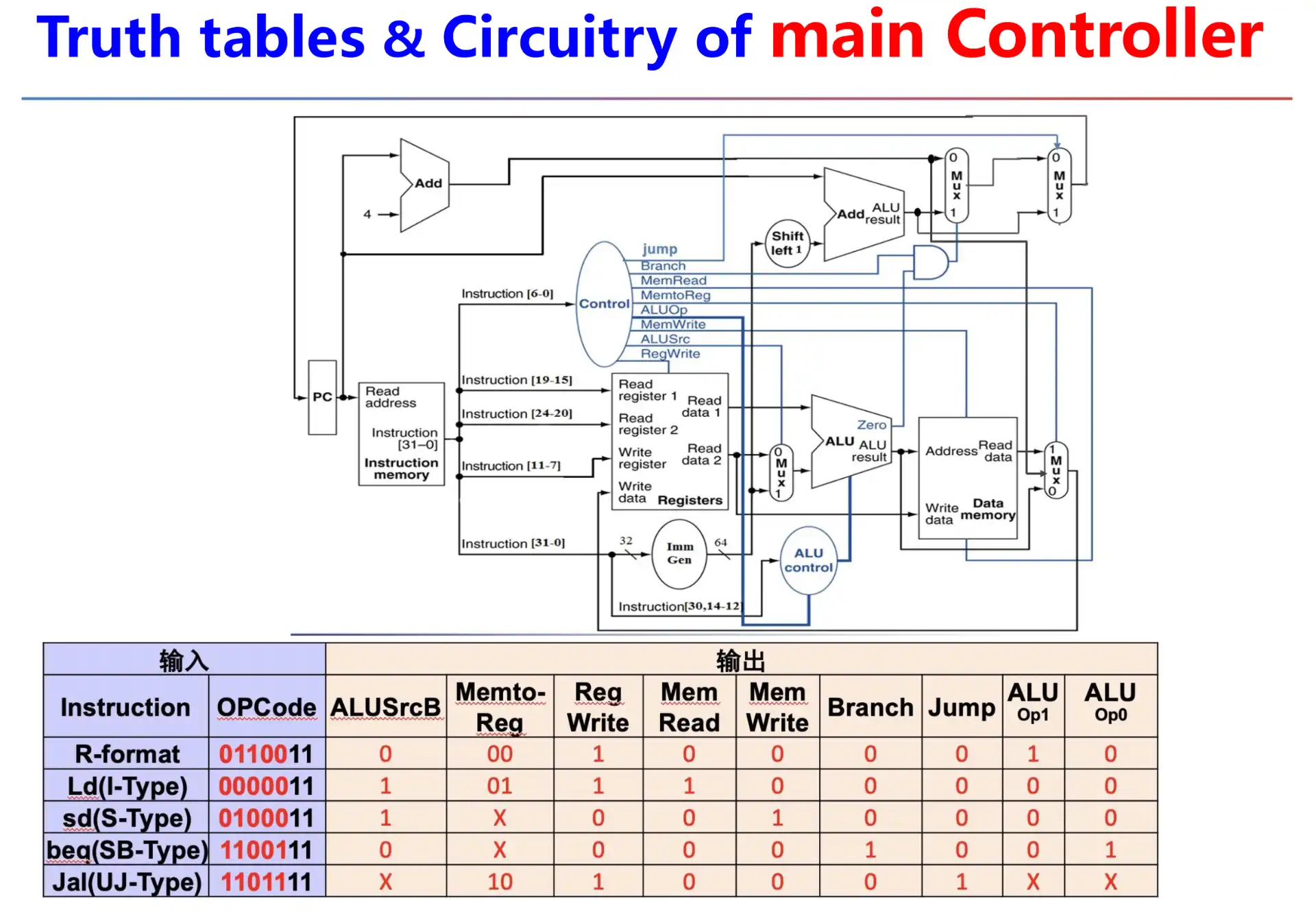

3 Control#

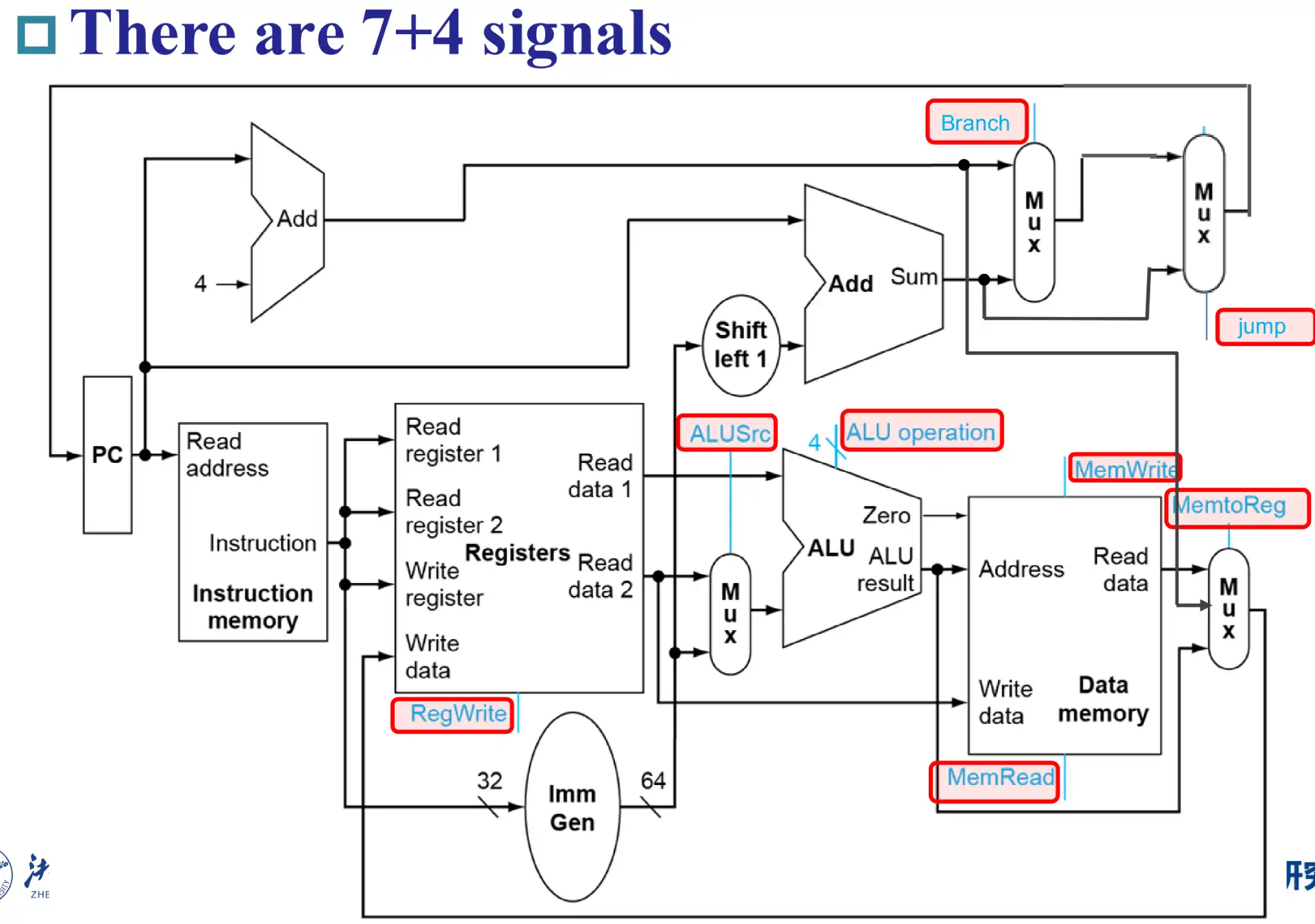

3.1 控制信号 7+4#

-

7+4 控制信号

- 7 个单独的信号

- 4 位 ALU 控制信号

-

图中

ALU_zero没有连接PCSrc,当然ALU_zero也不属于控制信号

-

和书上不同,

MemtoReg应该是两位的 -

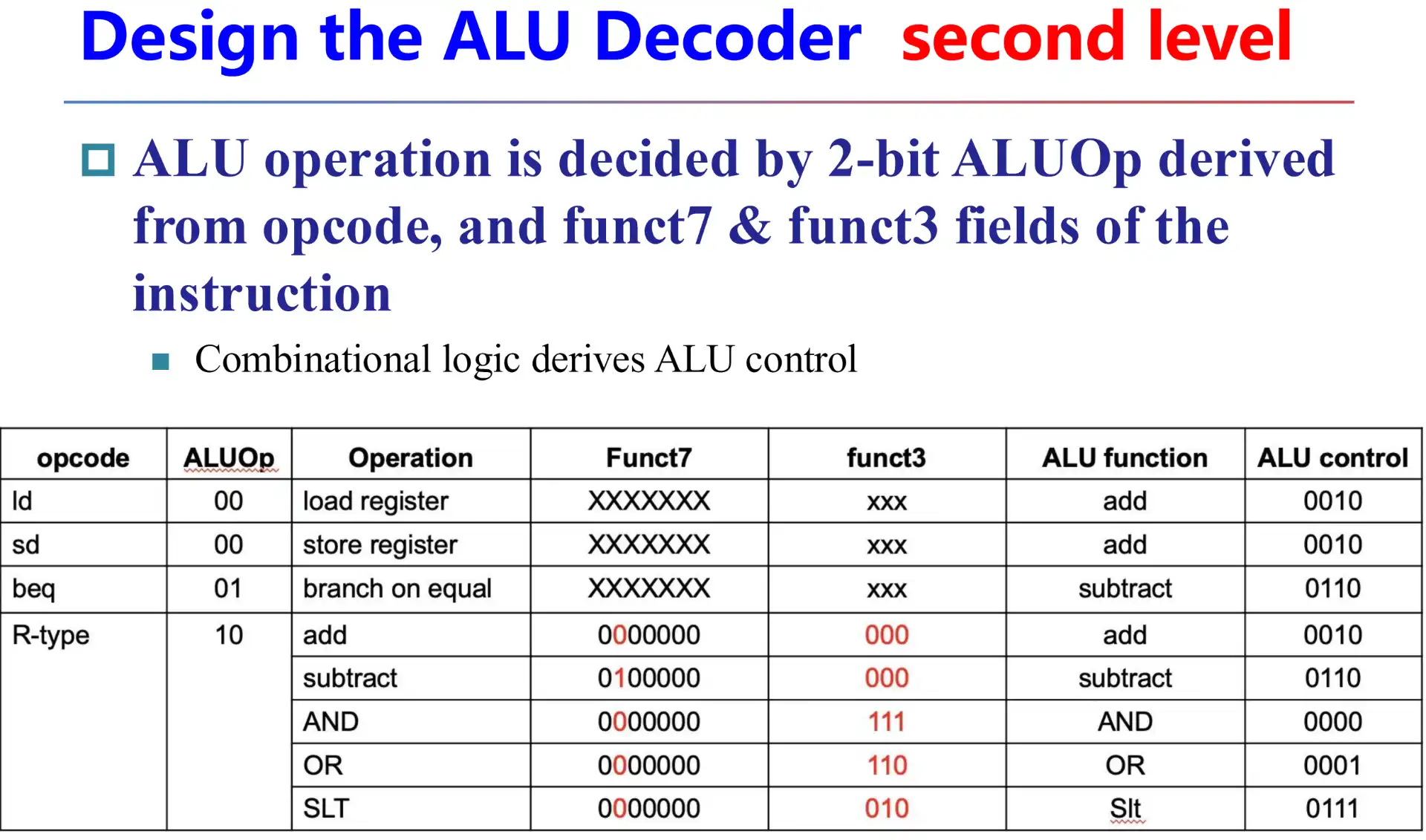

注意二级译码,

ALUop信号是ALUController二级译码产生的信号

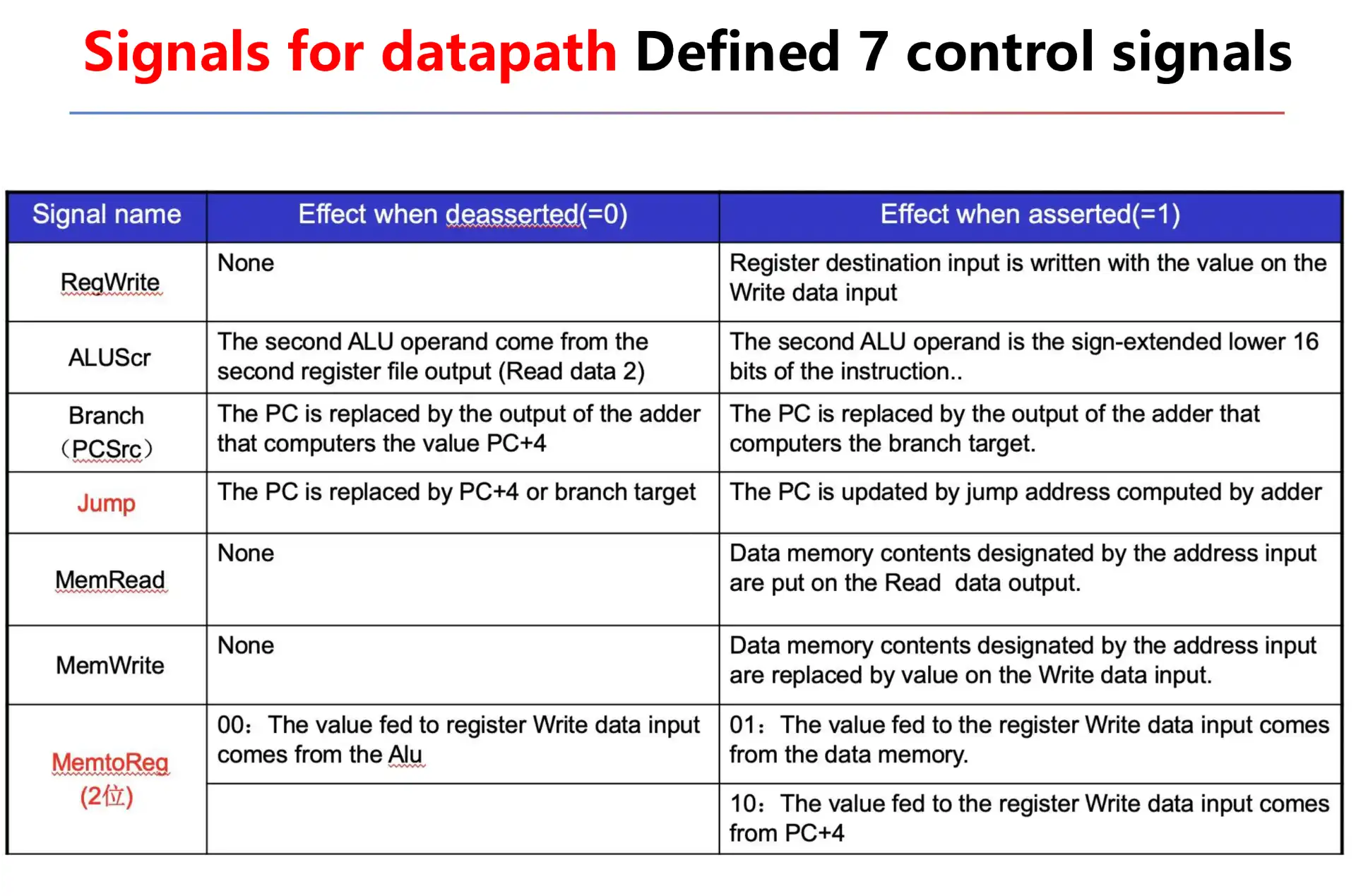

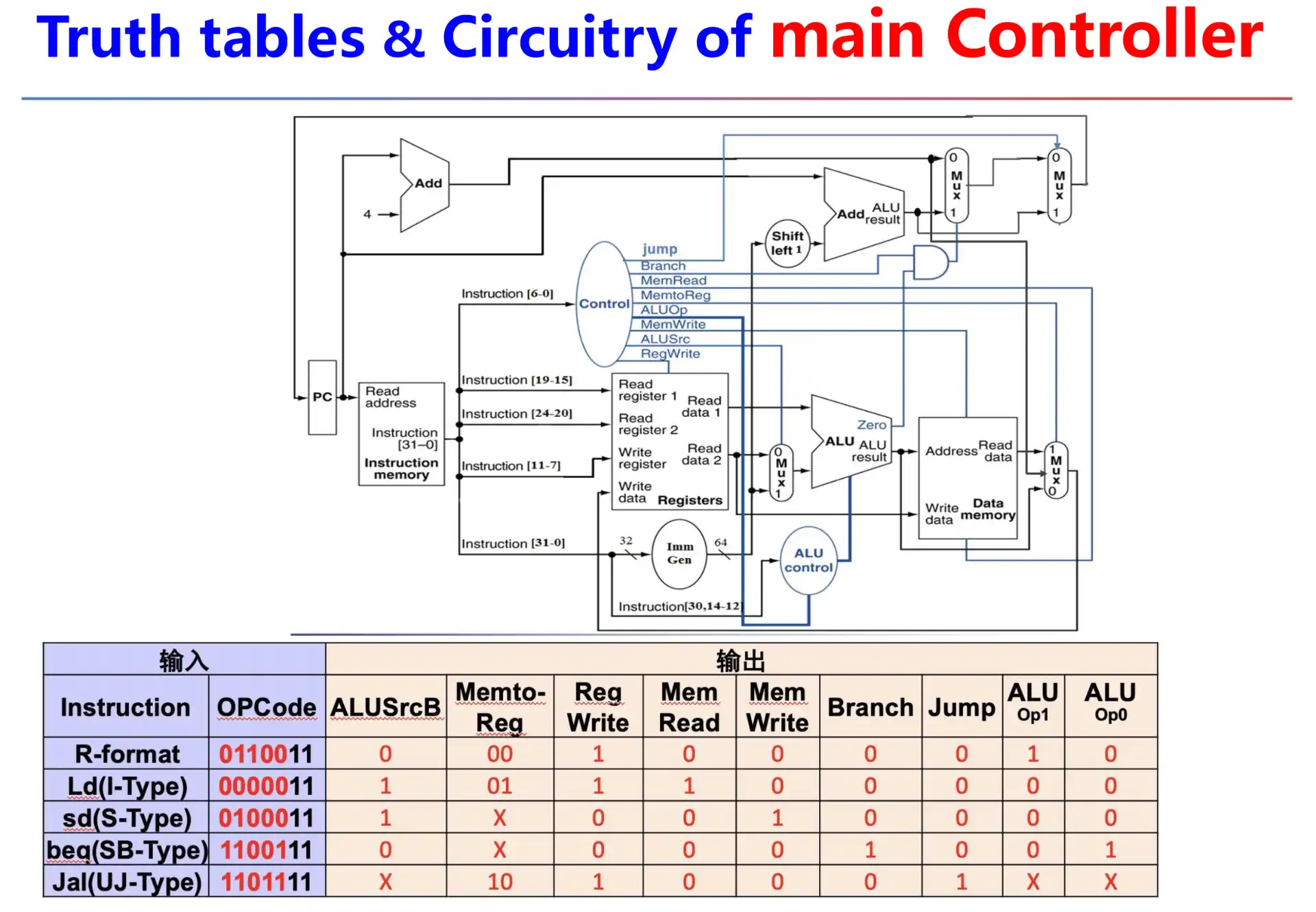

3.2 完整的 control#

-

一定要记住的一张图

- 这里使用了二级译码,

control输出的ALUOp是 2 位的 - 关于

X的情况sd, bep都不写入寄存器,RegWrite = 0,所以MemtoReg = don't carejal不需要主 ALU 的任何操作,所以ALUSrcB = ALUOp = don't care

- Instruction memory & Data memory

- 从处理器的视角,有利于提高吞吐量

- 但是在实际内存中是共享的,只是缓存映射不一样

3.2.1 关于二级译码#

3.3 更多分析题#

4 Conclusion#

-

记住下面两张图